- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC16C765T-I/L (Microchip Technology)IC MCU OTP 8KX14 USB 44PLCC

PIC16C745/765

DS41124C-page 110

Preliminary

2000 Microchip Technology Inc.

13.8

Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip dedi-

cated oscillator, which does not require any external

components. The WDT will run, even if the clock on the

OSC1/CLKIN and OSC2/CLKOUT pins of the device

has been stopped, for example, by execution of a

SLEEP

instruction.

During normal operation, a WDT time-out generates a

device RESET (Watchdog Timer Reset). If the device is

in SLEEP mode, a WDT time-out causes the device to

wake-up and resume normal operation (Watchdog

Timer Wake-up).

The WDT can be permanently disabled by clearing

configuration bit WDTE (Section 13.1).

13.8.1

WDT PERIOD

The WDT has a nominal time-out period of 18 ms

(parameter #31, TWDT). The time-out periods vary with

temperature, VDD and process variations. If longer

time-out periods are desired, a prescaler with a division

ratio of up to 1:128 can be assigned to the WDT under

software control by writing to the OPTION register.

Time-out periods up to 128 TWDT can be realized.

The CLRWDT and SLEEP instructions clear the WDT

and the postscaler, if assigned to the WDT. In addition,

the SLEEP instruction prevents the WDT from generat-

ing a RESET, but will allow the WDT to wake the device

from SLEEP mode.

The TO bit in the STATUS register will be cleared upon

a WDT time-out.

13.8.2

WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst

case conditions (VDD = Min., Temperature = Max., and

max. WDT prescaler), it may take several seconds

before a WDT time-out occurs.

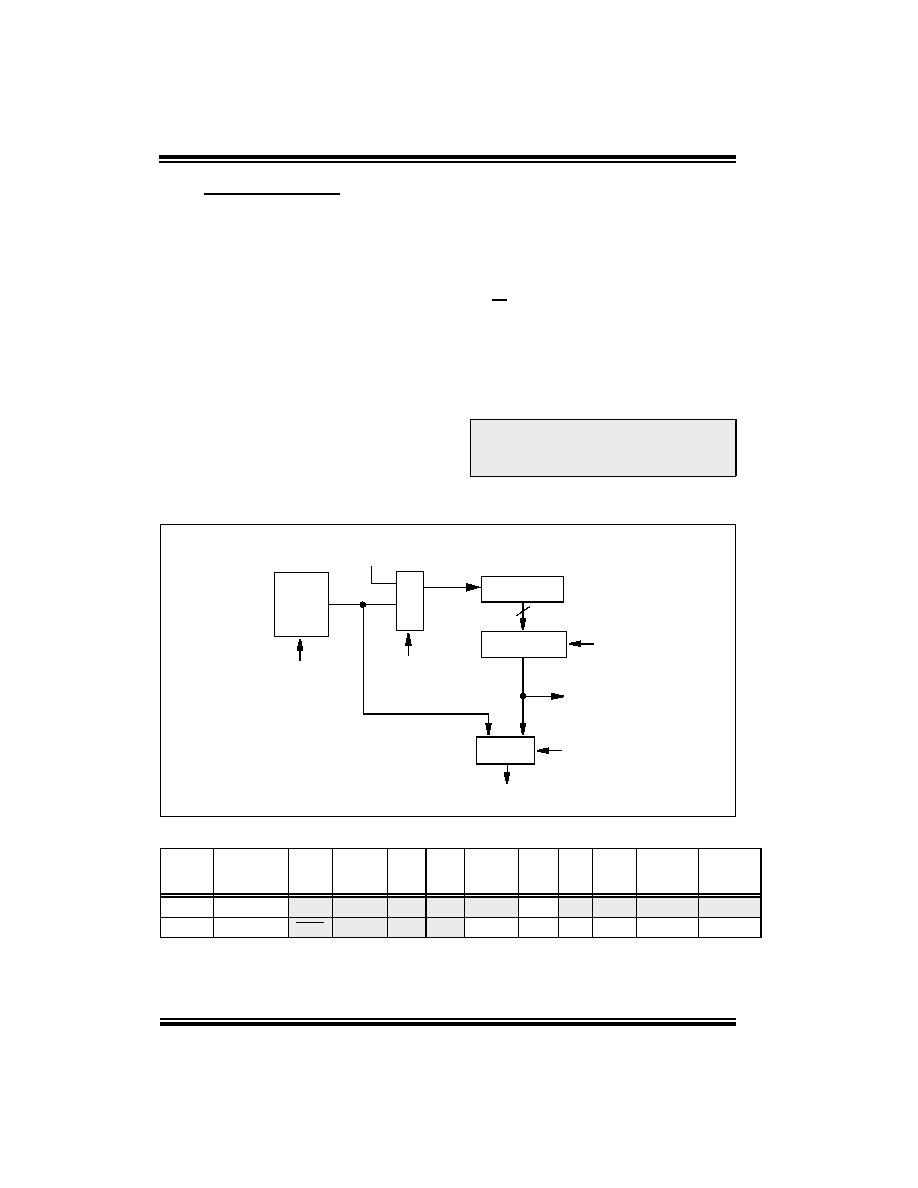

FIGURE 13-7: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 13-8:

SUMMARY OF WATCHDOG TIMER REGISTERS

Note:

When a CLRWDT instruction is executed

and the prescaler is assigned to the WDT,

the prescaler count will be cleared, but the

prescaler assignment is not changed.

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on

POR, BOR

Value on

All Other

Resets

2007h

Config. bits

—

BODEN(1)

CP1

CP0

PWRTE(1)

WDTE

PLL

FOSC0

81h,181h

OPTION_REG

RBPU

INTEDG

T0CS

T0SE

PSA

PS2

PS1

PS0

1111 1111

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1:

See Register 13-1 for operation of these bits.

From TMR0 Clock Source

To TMR0 MUX

Postscaler

WDT Timer

WDT

Enable Bit

0

1

M

U

X

PSA

8 - to - 1 MUX

PS<2:0>

0

1

MUX

PSA

WDT

Time-out

Note: PSA and PS<2:0> are bits in the OPTION register.

8

745cov.book Page 110 Wednesday, August 2, 2000 8:24 AM

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18C442T-E/L

IC MCU OTP 8KX16 A/D 44PLCC

PIC16C621A-40/SS

IC MCU OTP 1KX14 COMP 20SSOP

PIC16C622A-40/SS

IC MCU OTP 2KX14 COMP 20SSOP

PIC16CE623-30/SO

IC MCU OTP 512X14 EE COMP 18SOIC

PIC16CE624-30/SO

IC MCU OTP 1KX14 EE COMP 18SOIC

PIC16CE624-30/SS

IC MCU OTP 1KX14 EE COMP 20SSOP

PIC16CE623-30/SS

IC MCU OTP 512X14 EE COMP 20SSOP

PIC16CE624-30/P

IC MCU OTP 1KX14 EE COMP 18DIP

相关代理商/技术参数

PIC16C765T-I/PT

功能描述:8位微控制器 -MCU 14KB 256 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-04/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-04E/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-04I/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-10/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-10E/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-10I/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-20/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT